PlatformIO Labs Helps Imagination Technologies Improve RISC-V Computer Architecture Training

New course removes complex, expensive, or vendor-specific tool barriers while working with RISC-V IP Cores and FPGAs

RISC-V has been described as the “open silicon” of the technology revolution spurred by open hardware and open software. The ability to understand and innovate upon computer architectures has been a weak element of academic research and collaborative professional communities due to the typical proprietary nature of chip designs. Now open architectures can be combined with open hardware and software to provide unique and advanced solutions to tackle problems in our rapidly growing and complex technological world.

Due to the increasing popularity of RISC-V within the semiconductor industry, Imagination Technologies and Western Digital have teamed up to sponsor the development of new RISC-V centered coursework, designed by academics, for academics. The goal of this coursework is to provide top quality materials and an equity of opportunity to learn from them to students globally. PlatformIO Labs was chosen to support this coursework because of its open source tooling that provides best-of-breed quality for the embedded hardware industry, because of it being easy to use, because it seamlessly integrates with modern development editors such as VS Code.

More and more companies have announced or have already extended their portfolio with new RISC-V products. Popular commercial and open source Real-Time Operating Systems (RTOS), debuggers, and compilers are adding support for cutting-edge RISC-V hardware. The RISC-V ISA is open source, vendor agnostic, and flexible enough to satisfy the growing demand for complex embedded systems. Because of these qualities, the RISC-V ISA is a perfect choice for FPGA soft processor designs, which will further enable RISC-V to gain increased adoption within the embedded systems industry and academic community.

This growing adoption fuels the need for approachable and in-depth educational materials, especially to satisfy the increasing need and global benefits available through remote learning. It’s crucial for the RISC-V community to collaborate with universities and other academic partners to develop comprehensive curricula so undergraduates will have a deep fundamental knowledge of modern real-world computer architectures.

While RISC-V adoption is on the rise, one challenge is the currently arduous development environment associated with the architecture. When working with FPGAs, developers rely on convoluted instruments simply to evaluate and interact with their RISC-V designs on real hardware. Working with FPGAs can be a daunting task even for seasoned developers, not to mention students and newly graduated specialists. The industry needs an open-source and easy-to-use development environment that covers all sets of common tasks (debugging, testing, simulating, etc.) that engineers perform on a daily basis when working with deployed designs.

PlatformIO satisfies this need to bring top quality development tools to the RISC-V community, without being vendor-specific, without a hefty financial barrier, and without being locked behind the wall of a proprietary software license.

About Imagination University Programme

Imagination Technologies offers a complete course on RISC-V computer architecture titled “RVfpga: Understanding Computer Architecture”. It includes a rich set of teaching materials and practical exercises to help students understand the key elements of processor architecture, including IP cores, and how to modify a RISC-V core and its microarchitectures.

The initial course consists of 10 labs with detailed instructions, examples, short questions, and hands-on exercises with solutions, giving teachers the flexibility to choose between a practical and an exam-based structure for the course. The course uses the Chips Alliance’s SweRVolf SoC, which is based on Western Digital’s RISC-V SweRV EH1 core. SweRV is one of the most developed cores in the RISC-V market that’s fully verified and ready for production.

The RVfpga course was created by Dr. Sarah Harris, Associate Professor of Electrical and Computer Engineering at University of Nevada, co-author of the popular “Digital Design & Computer Architecture” textbook, and Dr. Daniel Chaver-Martínez, Associate Professor of Department of Computer Architecture and System Engineering at Universidad Complutense de Madrid (Spain). The course engaged several widely reputed sponsors and supporters who have given outstanding support to this large and complex project. Key contributors are listed below.

PlatormIO Labs’ Contribution

One of the main missions of PlatformIO Labs is to bring together academics, developers, and silicon vendors, and to help them leverage modern open source software and hardware on anything from simple prototypes to truly groundbreaking projects, developed at any scale. We believe that when technology is open from top to bottom, that the collaboration afforded within such a community is the perfect place to explore new ideas and opens up tremendous opportunities. Our team is proud to be an active participant in this venture.

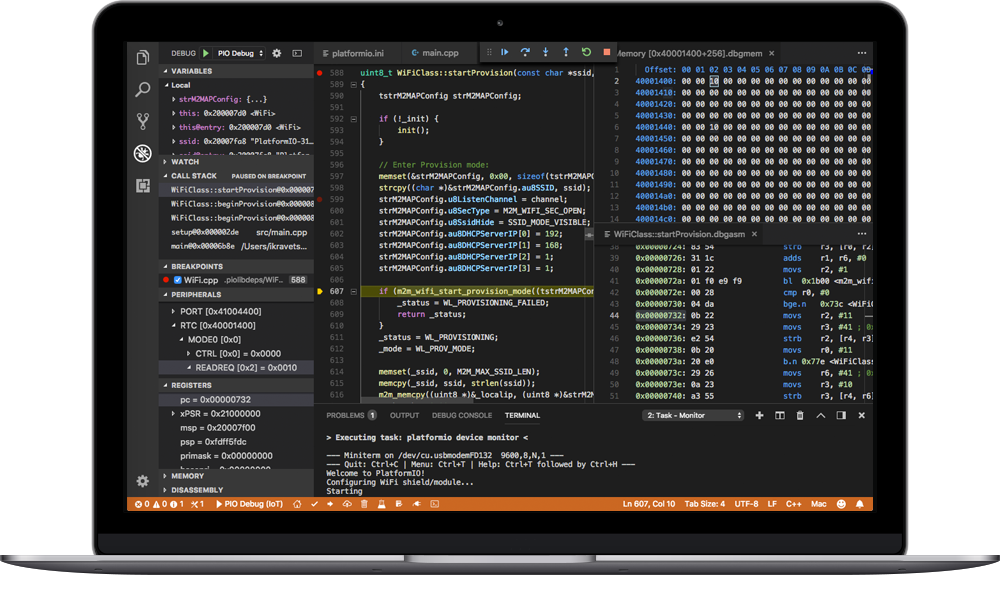

The RVfpga course uses PlatformIO — the open-source core of our Technology as a Service (TaaS) platform — for collaborative embedded development. PlatformIO’s development ecosystem integrates both hardware and software aspects of the course. Its open source license and flexible design are constantly being adapted to keep up with industry advancements. Students can avoid the burden of setting up unique, expensive, or vendor-specific tooling, and instead easily jump right in with a proper development environment and proceed directly to interacting with their RISC-V soft processors.

The main contributions of our work are the following:

- Powerful Unified Debugger. The integrated debugger supports both real hardware and hardware simulators (Whisper-ISS, Verilator), so that students can easily switch to a mixed-mode disassembly view to evaluate symbols, registers, and complex expressions, in watch windows.

- Trusted Package Registry. The registry quickly and securely delivers pre-built packages to students and professionals worldwide. Just-in-time, only what is needed, and fully automated downloads of dependent packages is an essential feature when it comes to online delivery of the curriculum, and ease of getting started for the students.

- In-depth Memory Analysis. A user-friendly UI allows students to access memory stores and get deeper insight into the internal application structure.

- PlatformIO Home. Like a welcoming dashboard, the PlatformIO Home page makes it easy for anyone to get started. It provides easy access to a comprehensive set of documentation and examples that were created specifically for this course, together with the main authors.

A Quick Tutorial

To demonstrate PlatformIO Labs’ contribution to this course and to show how PlatformIO reduces the usual complexity of executing ASM/C/C++ code in the RVfpga course, we are providing a short tutorial below. This tutorial shows how to import a project example, starting from the PlatformIO Home page, and how to run it even without hardware, by using an Instruction Set Simulator (ISS) called Whisper. This brief tutorial assumes you have already installed the PlatformIO IDE extension for Visual Studio Code. If you do not have the PlatformIO IDE installed, please follow these instructions before continuing with the tutorial.

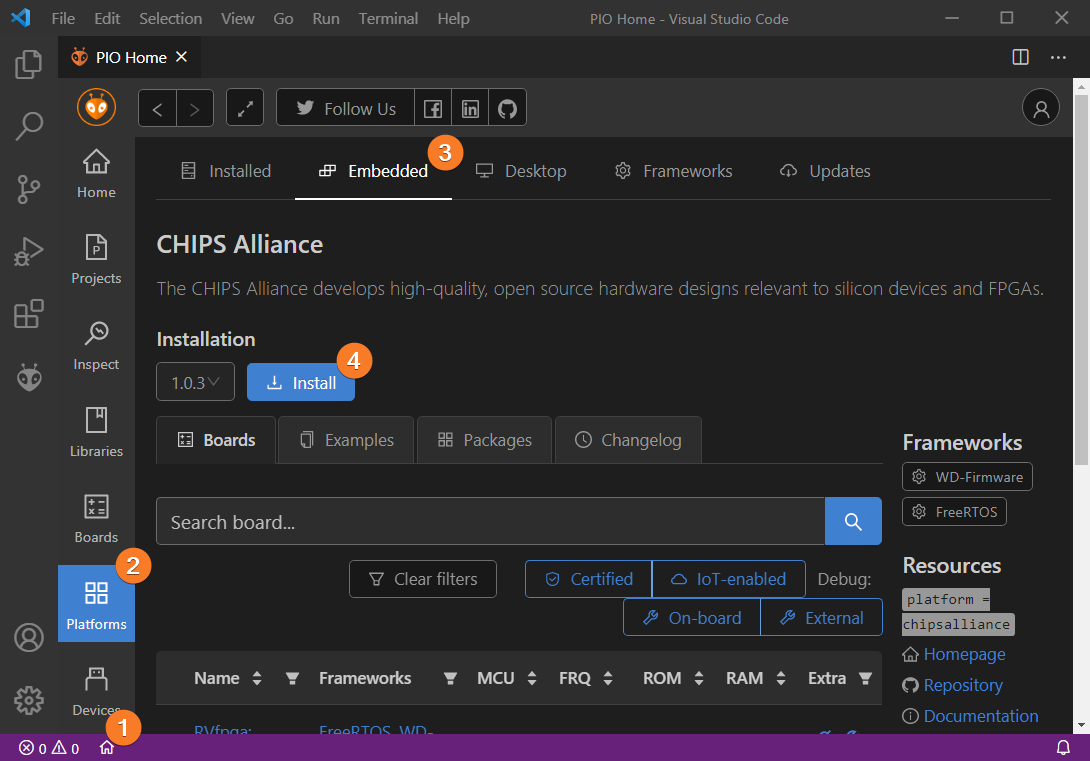

Installing CHIPS Alliance Development Platform

To start developing for the SweRV core you first need to install the CHIPS Alliance dev-platform from PlatformIO Home. Click on the icons near the numbers highlighted in orange, from 1 to 4. Note that at step 3 you will need to input “CHIPS Alliance” into the search string.

The above procedure shows how easy it is to set up a RISC-V development environment. PlatformIO will do all the heavy lifting for us by installing everything that is needed (toolchains, frameworks, etc.) automatically. When the one-click “Install” method is complete, a dialog window will pop up to tell you that the chipsalliance platform has been successfully installed.

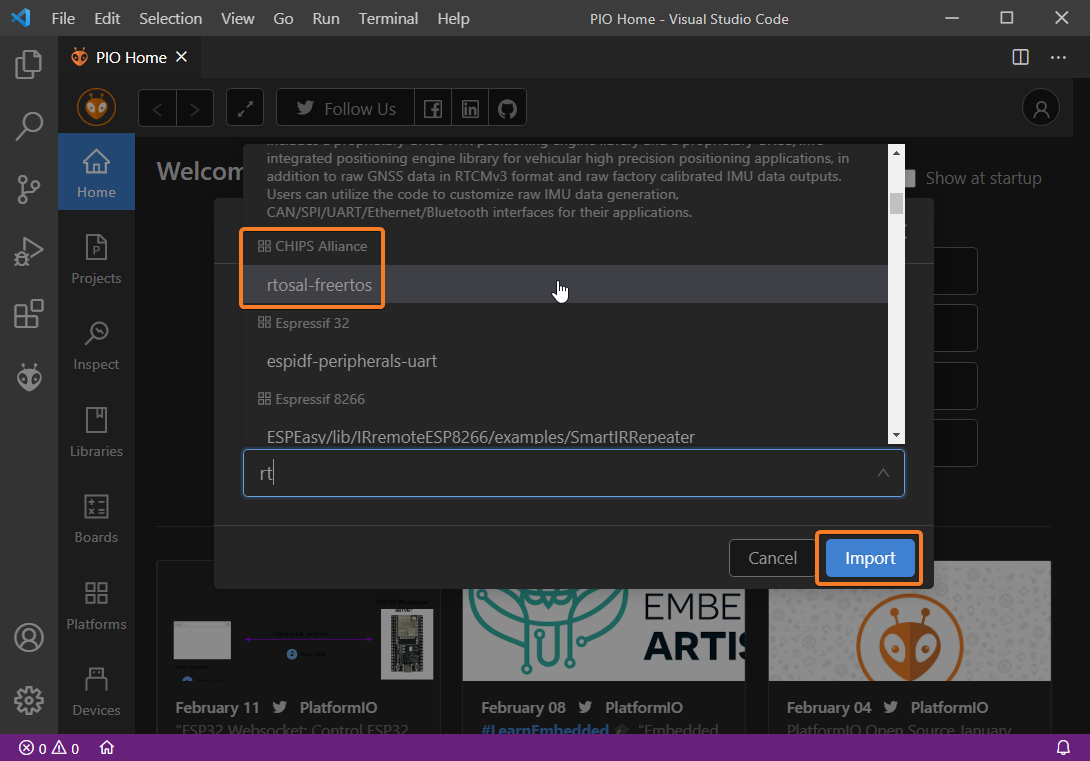

Importing and Compiling an Example

For the sake of simplicity, we will import one of the readily available examples prepared by the authors of the course. From the PlatformIO Home page, under the heading “Quick Access”, select the “Project Examples” button and select “rtosal-freertos” within the CHIPS Alliance platform, as shown in the image below.

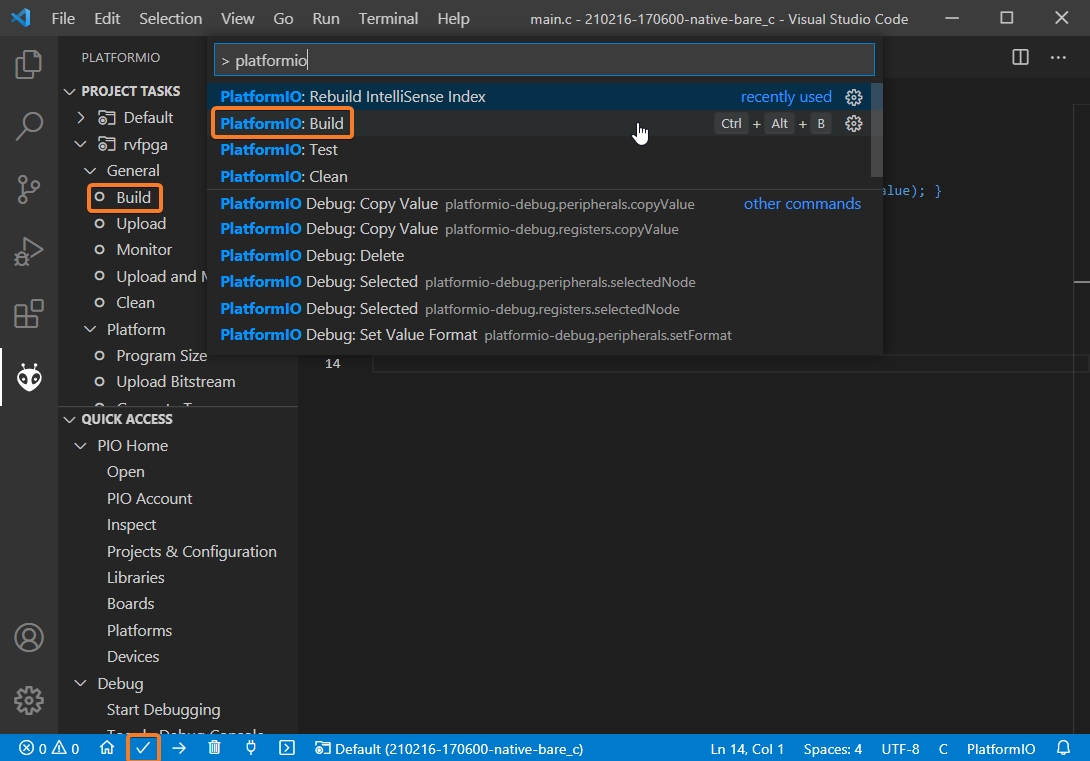

To build the project we can invoke different options, some of which are highlighted by an orange rectangle in the screenshot below. Simply use the method that feels most comfortable to you.

- Click the

Buildoption under the PlatformIOProject Tasksmenu on the left navigation column - Click the

✓icon (next to the home icon) toward the left side of the bottom blue PlatformIO Toolbar - From the VS Code top header menu, select and run

View: Command Palette... > PlatformIO: Build - From the VS Code top header menu, select and run

Terminal: Run Build Task... > PlatformIO: Build - Using the hot keys for your OS:

cmd-alt-b / ctrl-alt-b - From a terminal prompt at the command line by typing

pio run.

If everything went well, we should see the successful result in the terminal window.

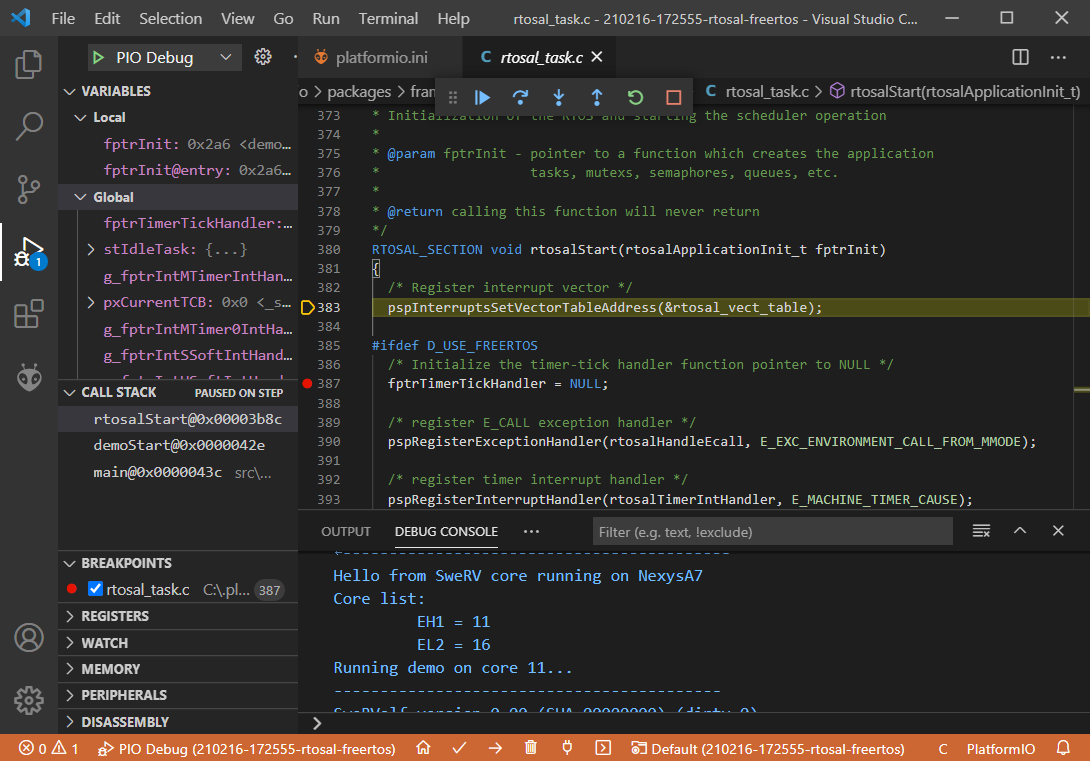

Debugging Experience

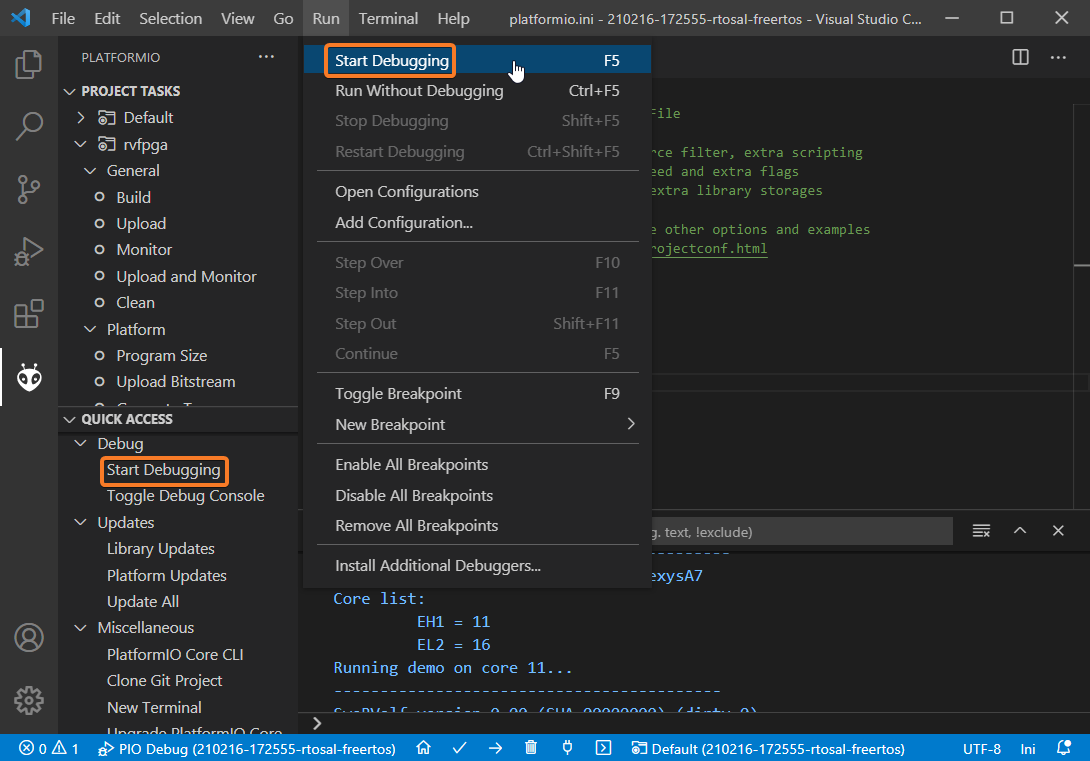

As we mentioned in the beginning of this tutorial, we will be using the Whisper ISS to debug the example. Configuring Whisper as the debug tool is as simple as adding one line to the platformio.ini file (which is located in the top level of the project folder, that you can find and open by clicking on it in the project file Explorer view):

platform = chipsalliance

framework = wd-riscv-sdk, freertos

board = swervolf_nexys

debug_tool = whisper

To start a debug session we can use one of the following options (the first two are highlighted in an orange rectangle in the screenshot):

- VS Code menu

Run > Start Debugging Start Debuggingoption fromPlatformIO > Quick Access > Debug menuF5hotkey

Once the debug session is started we can walk through the code using control buttons, set breakpoints, and add variables to the Watch window:

Note: this introductory tutorial only shows how to get started and execute a simple example using ISS as part of the RVfpga course. To understand the SweRV core in greater depth, please refer to the Imagination University Programme.

Conclusions

PlatformIO Labs is proud to partner with Imagination Technologies and Western Digital on the development and deployment of the RISC-V educational curriculum, as we firmly believe in the importance of collaboration between industry and academia. We are happy to see how our modern development instruments can enable an improved experience around these important educational materials. We hope that developers and students appreciate our efforts to support this combination of the RISC-V ISA, comprehensive teaching materials, and the opportunity to study the SweRVolf SoC. It’s even more fun to know that we are providing a more pleasant RISC-V learning experience for the academic community all around the world. We encourage all educational institutions to participate in the future growth of the RISC-V ecosystem.

About Imagination Technologies

Imagination was founded in 1985 and is one of the UK’s leading success stories as a developer of highly advanced intellectual property (IP) that creates considerable value in the electronic systems value chain, and ultimately improves the user experience in many different consumer electronic devices, including games consoles, mobile phones, and cars. Imagination Technologies has over 25 years of experience in designing and licensing market-leading processor solutions for graphics and vision & AI processing that offer strong differentiation compared to competing solutions for our customers.

About PlatformIO Labs

PlatformIO Labs is the corporate sponsor behind the PlatformIO open-source project. PlatformIO is a next-generation, professional collaborative platform for embedded development that enables customers to save resources and time by vastly reducing the expenses and labor associated with creating and maintaining product software. Its modern architecture is unmatched in the embedded tools market, and the result benefits developers everywhere by simplifying complexity and increasing productivity. PlatformIO Labs is a privately-held company headquartered in Tallinn, Estonia and with an R&D branch in Ukraine. To learn more, follow them on LinkedIn, Twitter @PlatformIO_Org, or visit piolabs.com.